|

如何使用"YFF 系列"3 端子贯通滤波器来抑制噪声并减少 MLCC 的数量 随着电子设备的高速和高频化,用于噪声滤波和去耦的电容器需要更低的ESL(等效串联电感)特性。

此外,在汽车电气系统中,为了提高安全性、舒适性和信息娱乐化,对低ESL类型的需求也在增加。

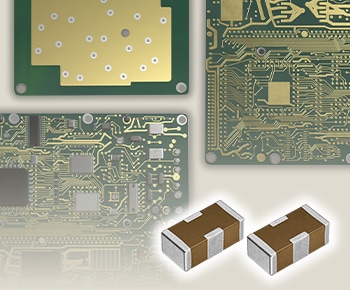

本解决指南介绍了使用TDK先进的低ESL元件3端子贯通滤波器“YFF系列”的各种解决方案。

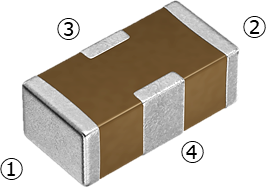

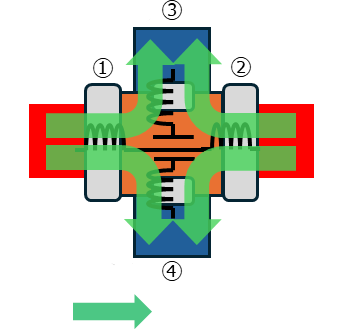

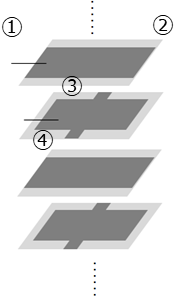

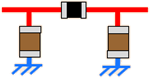

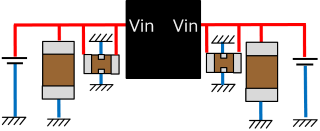

展示了3端子贯通滤波器的外观和内部结构的概念图。

它通常被称为3端子,但实际上是由两个端子电极和两个接地电极组成,内部则是由供电内部电极和接地内部电极交替堆叠而构成的。 贯通结构使得电容器与地面距离变短,有效降低了ESL并提高了噪声抑制效果。

由于有两个接地电极,并联可进一步降低ESL。 阻抗-频率特性与其他MLCC的比较作为抑制高频噪声的电容器须具有较低的ESR(等效串联电阻)和ESL以及较高的自谐振频率。

ESR和ESL是由端子电极和内部电极的电阻和电感值决定的。

因此,通过翻转(FLIP)普通2端子MLCC(多层陶瓷片式电容器)端子电极的长度方向和宽度方向,使电流方向变粗变短,可降低ESL,FLIP电容器也是应对噪声的有效措施。

与这种FLIP电容器相比,TDK的YFF系列3端子贯通滤波器具有更低的ESR和ESL。

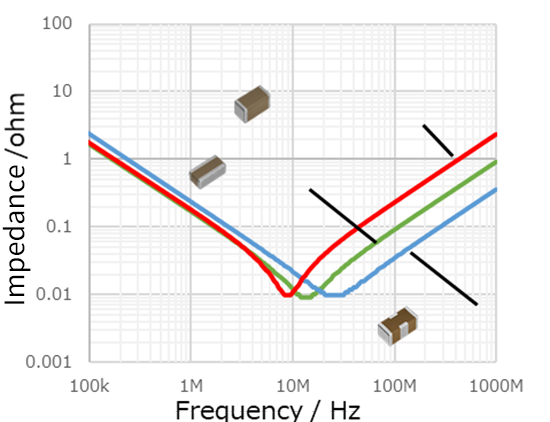

图2显示了TDK的2端子MLCC、FLIP电容器和3端子贯通滤波器的阻抗-频率特性和ESL值的单项比较。 约200~300pH约 80~100pH约 20~30pH 3端子贯通孔滤波器的ESL值低于普通2端子MLCC和FLIP电容器。 3端子贯通滤波器的应用及预期效果我们将介绍去耦、滤波器和 DC/DC 转换器应用的解决方案示例。 去耦应用中的解决方案示例电源线上的电压波动会使电路工作不稳定或产生噪声。因此,在电源线和地之间插入电容器,当负载突然变化时,电容器可临时提供电流以抑制电压波动。这称为去耦,使用的电容器称为去耦电容器。

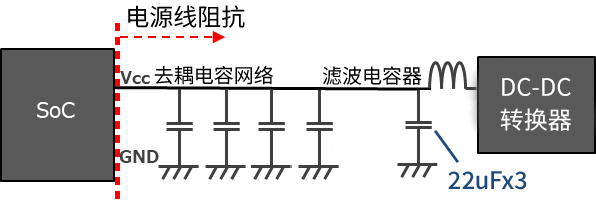

近年来,随着SoC的高功率化、高频化和小型化带来的低电压化,用于达到目标阻抗的去耦电容器的数量也有增加的趋势。YFF系列3端子贯通滤波器具有低ESL的特点,通过替代传统的2端子电容器,可有效减少元件数量

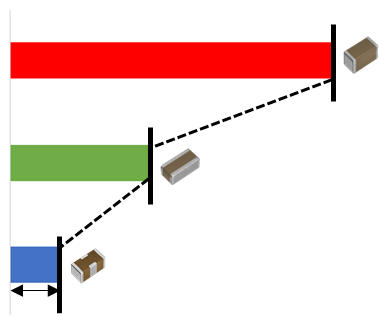

一般来说,为了降低宽频带中的阻抗,我们会将不同容值的MLCC多个并联。如下图所示,通过使用低ESL为特点的3端子贯通滤波器,可实现减少元件的使用数量。 2端子MLCC/1005mm(0402inch) /

1uF (1pc)2端子MLCC/1005mm(0402inch)1uF/

100nF/10nF/1nF (4pcs)3端子贯通滤波器/1005mm(0402inch) /

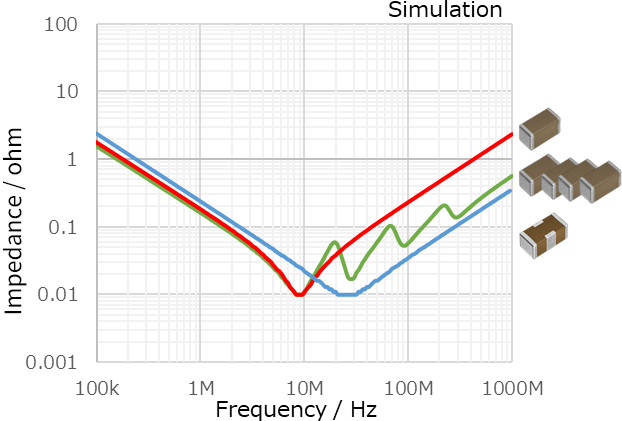

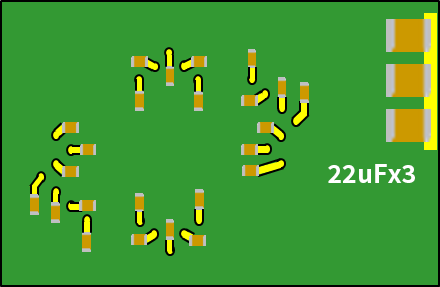

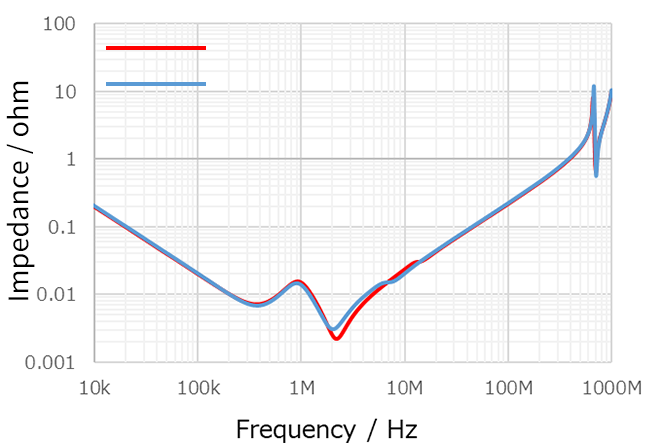

1uF (1pc) 使用PI模拟显示在去耦用途中通过3端子贯通型滤波器实现数量减少的事例。

比较从SoC端观察到的阻抗数据。

作为原有方案和改善方案中配置的共同点,假设前后均在DC/DC转换器上连接3个22uF MLCC,使DC/DC转换器平滑。 2端子1005mm (0402inch) x 24 pcs 3端子1608mm (0603inch) x 3pcs

3端子1005mm (0402inch) x 4pcs 可以看出,当前配置和TDK建议配置具有几乎相同的特性。 | 端子结构 | 型号

(mm/inch) | 容量

(uF) | 数量

(pcs) | 合计容量

(uF) | 占用空间

(mm2) |

|---|

| 2端子 | 1005/0402 | 1 | 16 | 16 | 8 |

|---|

| 2端子 | 1005/0402 | 0.1 | 8 | 0.8 | 4 |

|---|

| 当前配置 | 24 | 16.8 | 12 |

|---|

| 端子结构 | 型号

(mm/inch) | 容量

(uF) | 数量

(pcs) | 合计容量

(uF) | 占用空间

(mm2) |

|---|

| 3端子 | 1608/0603 | 4.7 | 3 | 14.1 | 3.84 |

|---|

| 3端子 | 1005/0402 | 1 | 4 | 4 | 2 |

|---|

| TDK建议配置 | 7 | 18.1 | 5.84 |

|---|

通过将2端子MLCC替换为3端子贯通滤波器,可减少贴装数量。但在实际线路上,会加上焊盘的电气成分,

所以去耦电容器的最佳数量构成会根据焊盘的不同而有所变化。

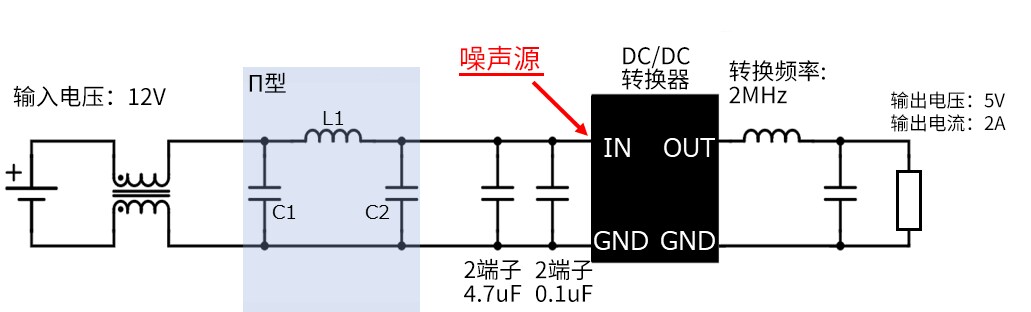

TDK免费提供通过PI仿真替换3端子贯通滤波器的仿真服务。详情请联系我们。 滤波器应用中的解决方案示例近年来,随着电源IC的高频化,高频噪声成为问题,是导致机组异常运行的原因。

作为噪声应对措施,一般通过在电源线上配置C-L-C π型滤波器来实施。通过在滤波器的电容器中加入3端子贯通滤波器,可以获得高衰减效果。

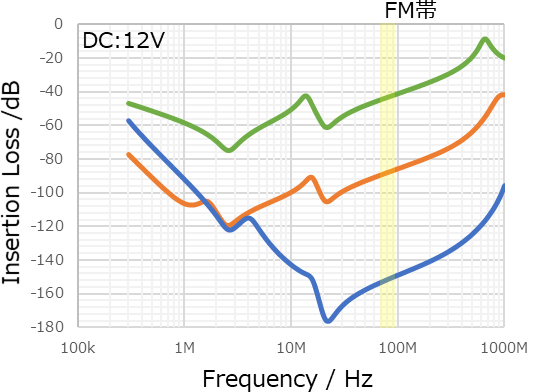

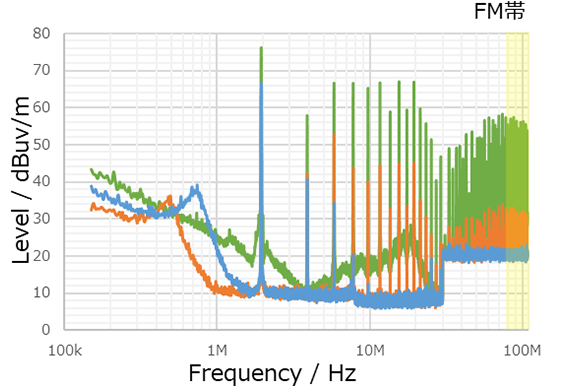

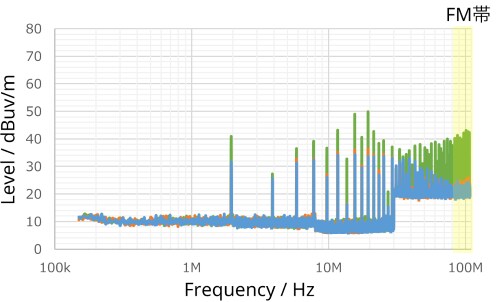

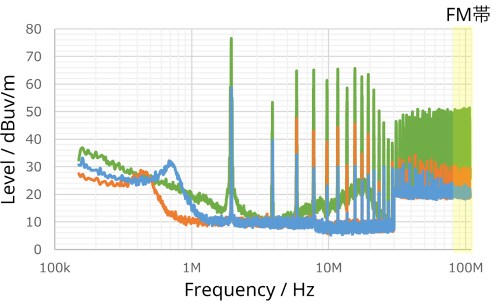

图8是通过模拟得出的传导特性的结果;而图9则是使用DC/DC转换器的实机测量了各噪声模式中产生的传导噪声(电压法)。

另外,关于图9的传导噪声电压法,3种构成都是作为共模对策,在安装了本公司共模滤波器的状态下进行了测定。 | Π型滤波器的配置 | 1 | 2 | 3 |

|---|

| 接线图 | ※没有Filter | | | | C1 | - | 2端子电容器

3216mm(1206inch) ,

4.7uF , 35V | 3端子贯通滤波器

3216mm(1206inch) ,

1uF , 100V , 6A

YFF31AH2A105M

贯通连接* | | L1 | - | 磁珠

2.0×1.2mm,

220Ω at 100MHz, 3A | 磁珠

2.0×1.2mm,

220Ω at 100MHz, 3A | | C2 | - | 2端子电容器

3216mm(1206inch) ,

4.7uF , 35V | 3端子贯通滤波器

3216mm(1206inch) ,

1uF , 100V , 6A

YFF31AH2A105M

贯通连接* |

图7:测量条件和电路图*插入损耗包括滤波器+2 端 MLCC 4.7uF+2 端 MLCC 0.1uF。 82MHz 比较 配置1 : -43dB 配置2 : -87dB 配置3 : -151dB -44dB-64dB在该DC/DC转换器的评估环境中,

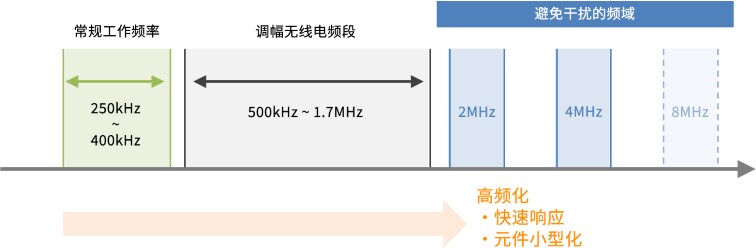

可以看出差模噪声很大。 82MHz比较 配置1 : 54dBuV/m 配置2 : 30dBuV/m 配置3 : 20dBuV/m -24dB-10dB特别是在差模噪声中,通过嵌入3端子可获得高噪声抑制效果。 通过在滤波器中嵌入3端子贯通滤波器,可在很宽的频率范围内获得高衰减效果。 DC/DC转换器应用中的解决方案示例DC/DC转换器的开关频率,能实现零件的小型化和高速响应,且为了避免对AM无线电频带造成干扰,如下高频化,从原来的数百kHz提高到2MHz以上的频率。

由此,波纹电压噪声和脉动噪声的频率也被高频化,所以需要寻求可达到数百MHz帯的高频领域的宽带噪音对策。

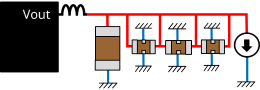

通过本事例,介绍在DC/DC转换器的输入侧、输出侧使用3端子贯通型滤波器来控制电源变动和减少数量的效果。 DC/DC转换器输入端附近配置3端子贯通滤波器的示例DC/DC转换器的输入端子由基频构成的N次谐波可能会因布线或IC寄生成分引起的开关噪声产生较大的高频噪声并辐射到外部电路。通常这个噪声必须从IC的根部切断,一般通过在IC附近放入小型的陶瓷电容器来解决,但我们将介绍使用3端子贯通型滤波器的DC/DC转换器的事例。另外,作为参考,本DC/DC转换器使用了3端子贯通型滤波器来抑制IC附近的噪声。两种配置的共同点是在输出电容器上配备了2端子MLCC 10uF。 | DC/DC转换器的规格 输入电压:5V 输出电压:0.8V SW频率:2MHz 输出电流:4A |

|---|

| 配置 | 2端子MLCC

1005mm/0402inch, 100nF,50V

x 1pc

*分流直通连接 | 3端子贯通滤波器

YFF18AC1A104M

1608mm/0603inch , 100nF ,10V

x 1pc

*分流直通连接 |

|---|

| 接线图 | | 电源一侧连接在内层 |

|---|

| 电路图 | | |

|---|

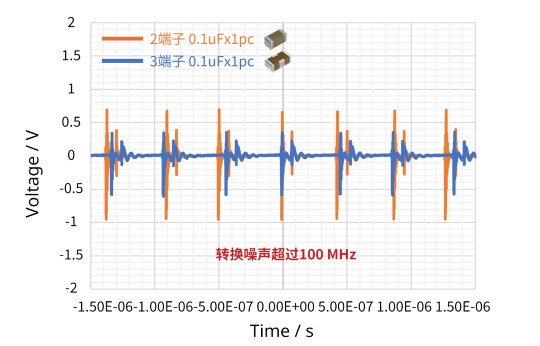

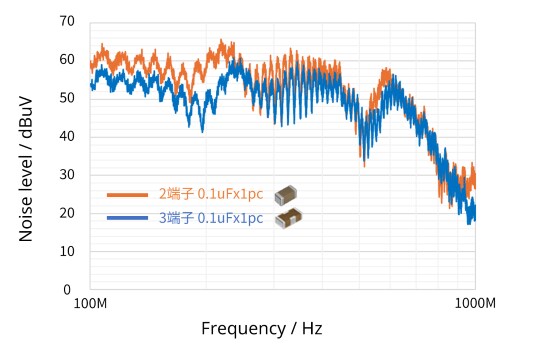

2端子

0.1uFx1pc

1.64Vpp

3端子

0.1uFx1pc

0.92Vpp

-0.72V2端子

0.1uFx1pc

65dBuVmax

3端子

0.1uFx1pc

60dBuVmax

-5dB在DC/DC转换器输出端配置3端子贯通滤波器的示例在DC/DC转换器的输出端,由基频组成的N次谐波以及由布线和IC寄生元件引起的开关噪声也会产生较大的高频噪声,并有可能辐射到外部电路。

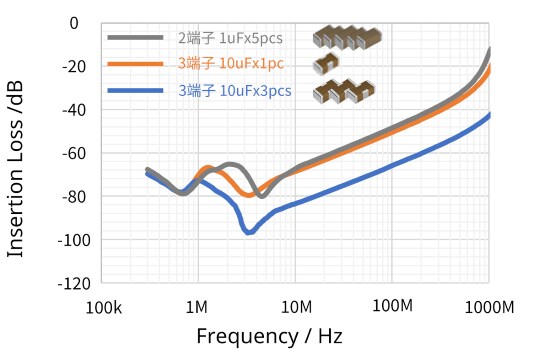

SoC 的低电压缩小了最大/最小电压裕量,而更复杂的设备对高频噪声越来越敏感。因此除了SoC方面的方法外,最好还能在噪音的根源电源IC方面采取措施。传统的有效噪声抑制方法是在多级中放置2端子MLCC,但我们将介绍使用TDK的大容量3端子直通滤波器来抑制电源波动的示例。这两种配置的共同特点是在输出电容器上配备了2端子MLCC47uFx1pc。 | 配置 | 2端子MLCC

1608mm/0603inch, 1uF, 16V

x 5pcs | 3端子贯通滤波器

YFF18AC0G106M

1608mm/0603inch, 10uF, 4V

x1 pc

*分流直通连接 | 3端子贯通滤波器

YFF18AC0G106M

1608mm/0603inch, 10uF, 4V

x3 pcs

*分流直通连接 |

|---|

| DC/DC转换器的规格 输入电压:5V 输出电压:1.8V SW频率:2MHz 输出电流:2A |

|---|

| 接线图 | | | |

|---|

| 电路图 | | | |

|---|

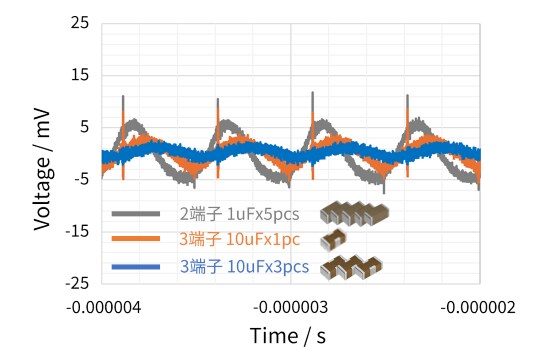

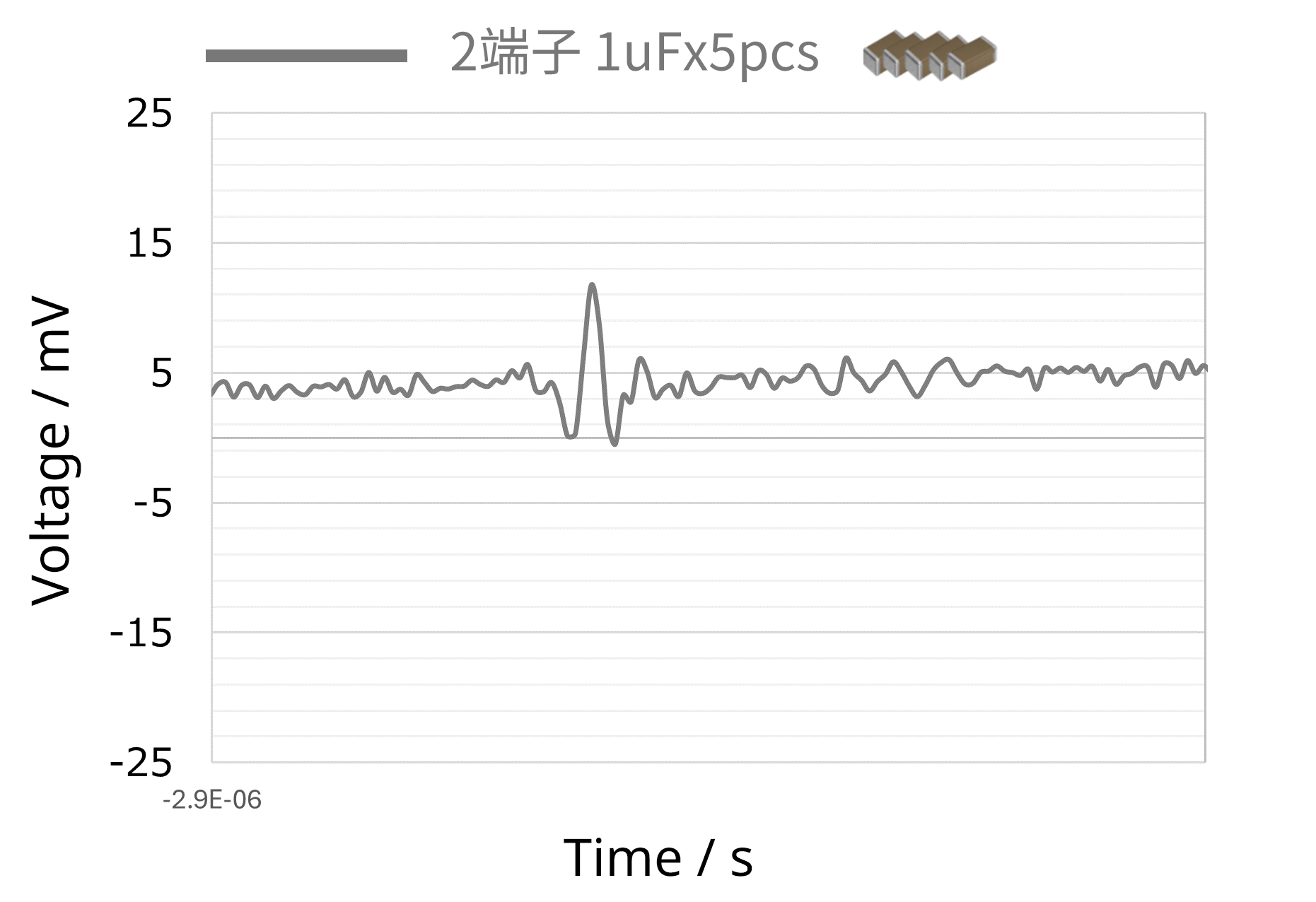

2端子

1uFx5pcs

-48.4dB

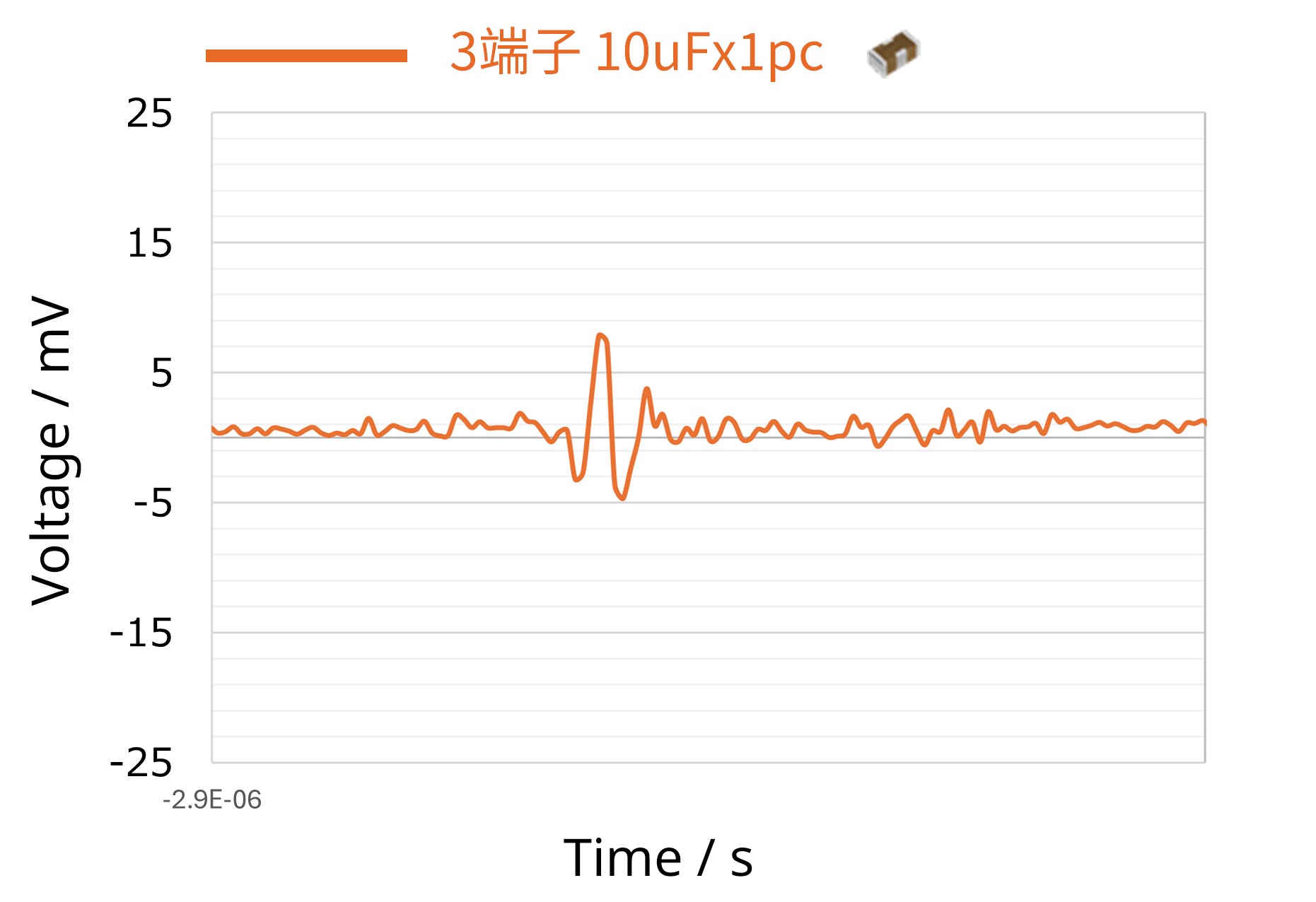

3端子

10uFx1pc

-50.5dB

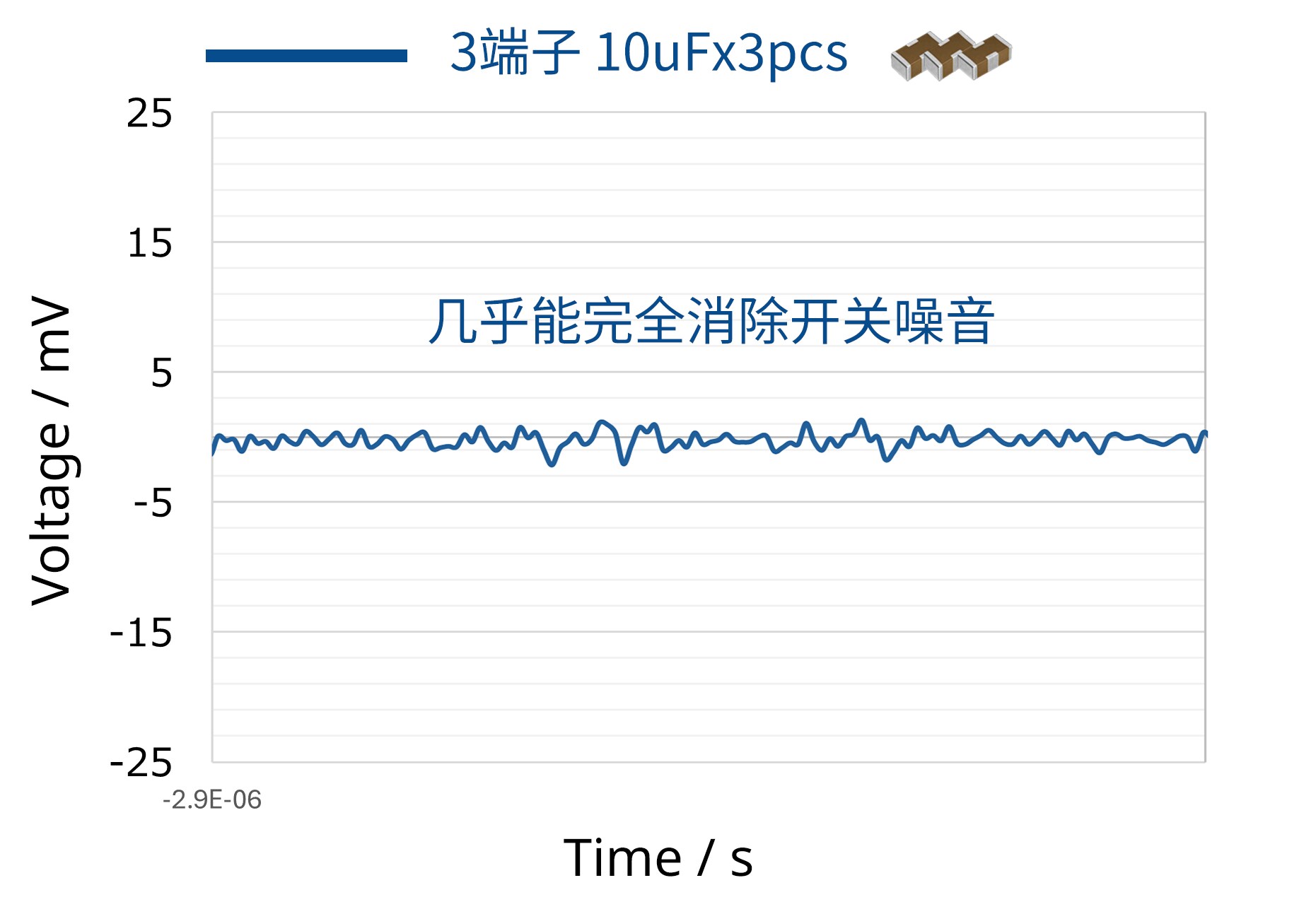

3端子

10uFx3pcs

-65.9dB

(100MHz比较)-2.1dB-15.4dB2端子

1uFx5pcs

19mVpp

3端子

10uFx1pc

15mVpp

3端子

10uFx3pcs

5mVpp

-4mV-10mV3端子可以取得高衰减的效果,可有效减少数量和改善特性。

通过3端子多个排列,获得高衰减的效果。 图13:插入损耗和电压波形比较将电压波形聚焦在开关噪声上。

通过将3端通滤波器的并联数量从1个增加到3个,几乎抑制了开关噪声。 通过搭载TDK的大容量3端子贯通滤波器,可以抑制振幅水平,元件数量有望减少。

另外,通过增加3端子的并联数,可以通过并联效果得到更高的衰减效果。

在本例中,并联3个3端子的配置3中几乎消除了高频转换噪声。 充分利用3端子贯通滤波器特性时的注意事项3端子贯通滤波器作为单品具有低ESL的特征,为了充分发挥其特征,减少接地设计和通孔引起的寄生成分是很重要的。

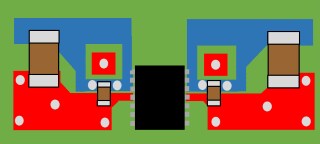

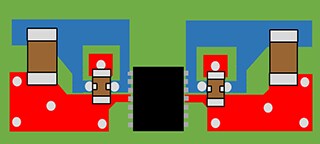

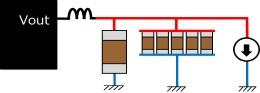

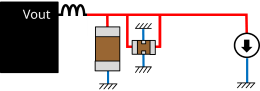

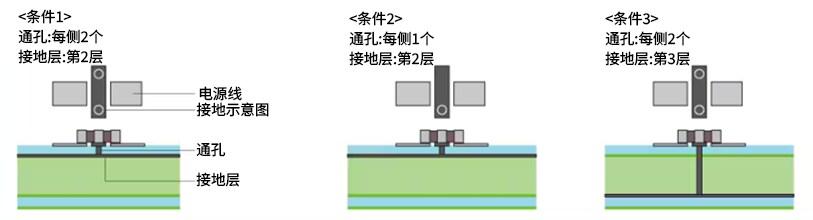

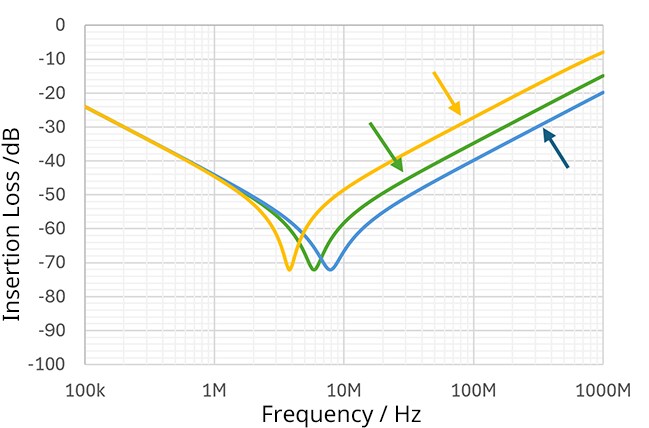

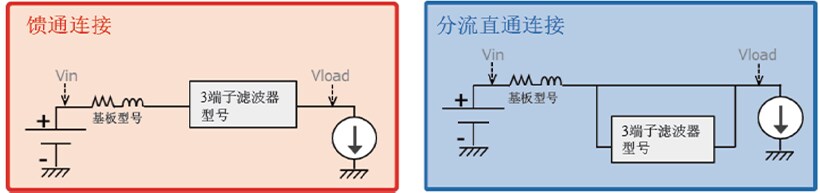

图15显示了连接接地设计和接地面的通孔的长度(深度)与3端子贯通滤波器的衰减-频率特性之间的关系。 通过模拟比较了以下条件①~③的安装条件。 在通孔为接地设计两端2个的情况下(条件①)和一侧1个的情况下(条件②),两侧2个表示较大的衰减量。另外,在两侧都有2个通孔且通孔长度较深(条件③)的情况下,通孔短(浅)的条件①表示较大的衰减量。 单个3端子贯通滤波器的特性 YFF15AC0J105M (1005mm(0402inch)/6.3V/1uF) 条件 ①条件 ②条件 ③为了充分发挥3端子贯通滤波器的特性,建议增加接地端的通孔,缩短通孔长度(深度)。 接线方法3端子贯通滤波器通常连接到电源线使用,但有两种接线方法。

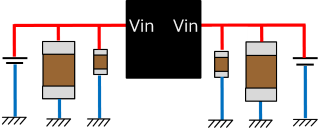

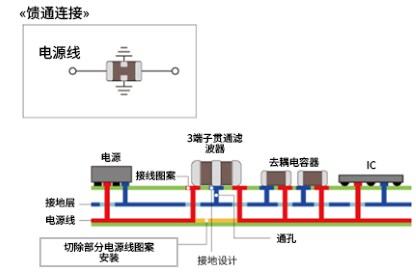

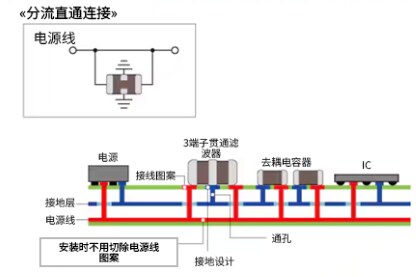

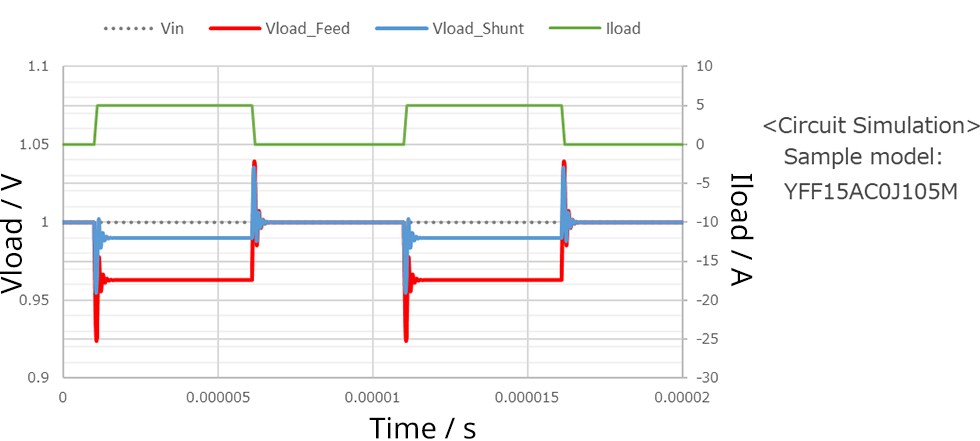

如图16所示,分别是与电源线串联的贯通连接和并联的分流直通连接。

下图显示了每个连接的示例。在本示例中,多层印刷电路板的第一内层用作接地面层,第二内层用作电源线层,

安装时通过通孔连接到每个接地面。对于贯通连接,切除部分电源线设计并安装;对于分流直通连接,安装时不需要切除电源线设计。

请确认总结各种接线方法的特征和主要用途的表格。 | | 贯通连接 | 分流直通连接 |

|---|

| 安装方法 | 切除抑制噪声的部分接线设计并将其插入滤

波器之间。 | 采用并联(分流)连接,无需改变线路的接

线设计。 |

|---|

| 主要用途 | 抑制高频带噪声

(过滤器应用) | 抑制IC电压波动

(去耦应用) |

|---|

| 优点 | 对于高频之前的宽带具有很好的噪声抑制效果。 | 芯片内部几乎无电流流过,因此不存在额定电流的限制。

未切除接线图案,因此即使在设计完电路板后也能轻松更改

数量。 |

|---|

| 缺点 | 电流在芯片内流动,因此存在额定电流的限 制。并且因为切除部分电源线/信号线设计, 所以后期很难改变设计。 | ESL略高于贯通连接。 |

|---|

| 噪声抑制效果 | ◎ | 〇 |

|---|

由于线路上的噪声必须通过芯片内部,因此

能有效地将噪声接地。 | 一部分的噪声通过电源线,因此噪声消除效果不如贯通连接。 | | 电压波动抑制效果 | △

(发生电压下降) | ◎

(电压下降较小) |

|---|

贯通连接比分流直通连接的电压降更大,但降噪效果更好。分流直通还可以抑制电源线的电压降,即使在低压电路中也可以使用。请参考上述比较表,选择适合用途的接线方法。 图17:贯通连接和分流直通连接的负载波动模拟比较(图像)总结YFF系列3端子贯通滤波器的特征是低ESL,由于降噪效果好,可以做滤波器、DC/DC 转换器或去耦使用,期待着元件数量减少和特性改善,因此需求不断增加。

|

|